Index

> Main > Intel AMX extension

Index

> Main > Intel AMX extension |

| Author |

|

|

Ali.Z 18 Jan 2022, 05:48

https://en.wikichip.org/wiki/x86/amx

not sure how old are these instructions, but AFAIK this is the latest extension. it looks like it could be useful for this type of software that does math, graphics and/or games. edit: also does fasm support these things _________________ Asm For Wise Humans |

|||

|

|

Tomasz Grysztar 18 Jan 2022, 12:01

The previous thread about it went completely off the rails.

I keep this extension in mind, I want to implement it, but with no hurry. I'm likely to start with a fasmg cpu/ext package, as this is generally the route I take these days. |

|||

|

|

sylware 18 Jan 2022, 22:16

isn't that risc-v gpu?

|

|||

|

|

Ali.Z 23 Jan 2022, 09:56

_________________ Asm For Wise Humans |

|||

|

|

ohara 02 Oct 2025, 16:42

Are AMX instructions in FASM yet?

|

|||

|

|

Tomasz Grysztar 02 Oct 2025, 16:53

ohara wrote: Are AMX instructions in FASM yet? |

|||

|

|

Tomasz Grysztar 03 Oct 2025, 14:18

Intel AMX instructions support for fasm2 is ready: https://github.com/tgrysztar/fasm2/commit/eee0e48d67ce97d0c3241a7f80937b0f2e11b9f9

Quick and dirty, but that's the advantage of fasmg-based implementation: rapid prototyping is easy. |

|||

|

|

Mаt Quasar 16 Oct 2025, 14:51

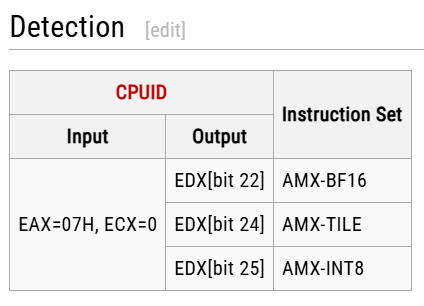

From the link posted by OP: https://en.wikichip.org/wiki/x86/amx, this is the CPUID detection.

|

||||||||||

|

||||||||||

< Last Thread | Next Thread > |

Forum Rules:

|